台积电助力欧盟首颗自主处理器流片 欧洲超级计算机计划迈出关键一步

作者: CBISMB

责任编辑: 张金祥

来源: ISMB

时间: 2025-07-16 11:00

关键字: Sipearl,台积电,Rhea-1

浏览: 284

点赞: 0

收藏: 0

欧洲处理器计划(EPI)的第一步已迈出,法国芯片设计公司Sipearl宣布,其自主研发的Rhea-1处理器已进入台积电流片阶段,首批测试芯片计划于2026年初交付合作伙伴。这一里程碑标志着欧盟在构建自主可控的高性能计算生态系统中迈出实质性步伐。

Rhea-1的使命与挑战

Rhea-1处理器专为德国于利希超级计算中心(JSC)的Jupiter超级计算机设计,将作为附加CPU模块部署,初期安装规模超过2600个处理器。尽管其5万亿次浮点运算性能仅占Jupiter总计算能力(1百亿亿次)的0.5%,但此次测试被视为欧盟摆脱对外部处理器依赖的关键试点。

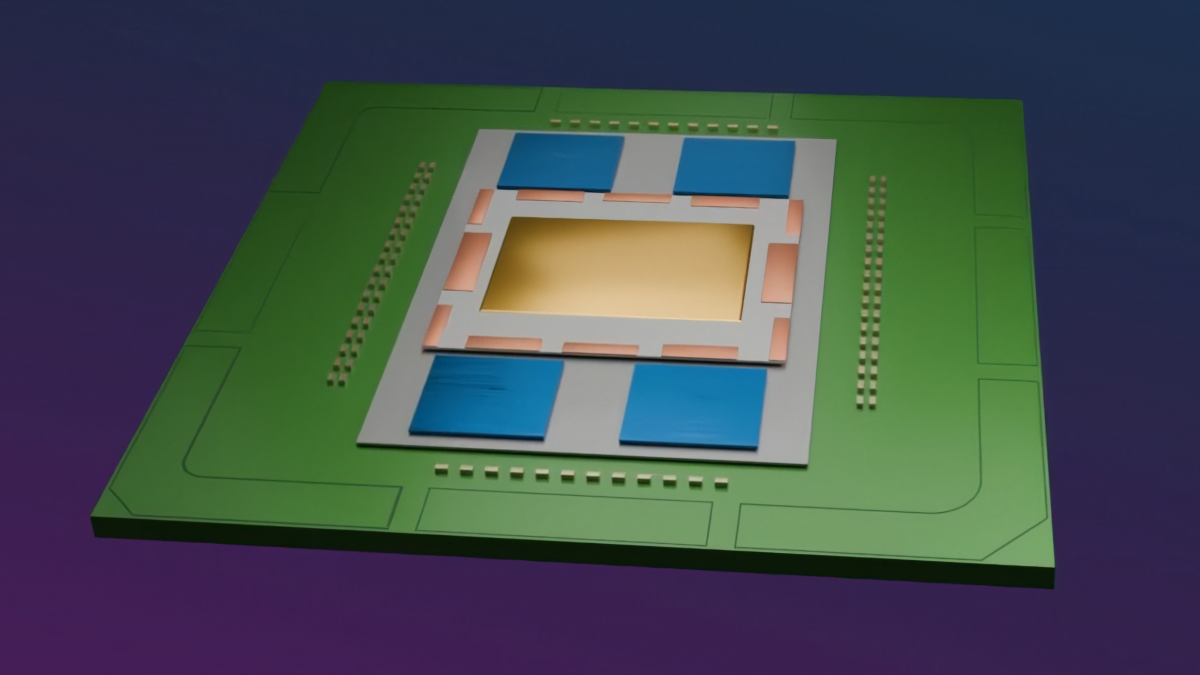

技术层面,Rhea-1采用台积电N6(7nm优化)节点制造,搭载Arm Neoverse V1核心,配备64GB HBM2e高速内存及512GB DDR5内存。然而,这一设计引发外界关注:相较于当前行业主流的3nm制程及即将量产的2nm、英特尔18A工艺,N6节点在能效比和性能密度上已显滞后。业内分析指出,Rhea-1的架构设计可追溯至2021年规划初期,当时该方案尚属前沿,但随技术迭代加速,其继任者Rhea-2的升级已迫在眉睫。

多元代工布局提速 Rhea-2的期待

尽管Rhea-1选择台积电作为合作伙伴,欧盟正积极推动本土半导体产业链建设。除台积电计划扩大欧洲产能外,英特尔代工厂亦被纳入潜在合作名单,其18A制程理论上可满足欧盟中期生产需求。这种多源代工策略旨在降低供应链风险,同时为CPU制造商提供更多本地化选择。

Sipearl虽未公开Rhea-2的具体规划,但业内推测其将采用更先进的制程节点与芯片组设计,以适配未来超级计算机对能效和算力的严苛要求。JSC项目负责人表示,Rhea-1的测试经验将为欧盟积累关键数据,推动处理器架构与超级计算机系统的深度优化。

此次合作不仅验证了欧盟在高端芯片设计领域的潜力,也为全球半导体产业格局多元化注入新动力。随着Rhea-1流片推进,欧洲距离实现“自主超级计算机”战略目标正渐行渐近。