千亿之战打响:HBM4 决定人工智能未来格局

作者: CBISMB

责任编辑: 张金祥

来源: ISMB

时间: 2025-10-20 11:44

关键字: 千亿市场,HBM内存,人工智能,市场份额

浏览: 1373

点赞: 65

收藏: 13

在生成式人工智能革命的浪潮下,一场围绕高带宽内存(HBM)的千亿美元内存战争正激烈上演。这场战争不仅关乎当下,更将决定未来人工智能领域的主导权,而 HBM4 技术则成为这场战争的关键“武器”。

内存带宽成 AI 发展关键瓶颈

生成式人工智能的蓬勃发展,让原始计算能力的重要性愈发凸显。然而,在拥有数千个 GPU 的庞大 AI 数据中心里,处理速度并非真正的瓶颈,内存带宽才是决定 AI 基础设施能否有效发挥作用的关键因素。如果无法快速移动数据,价值数万亿美元的人工智能基础设施将沦为昂贵的“镇纸”。

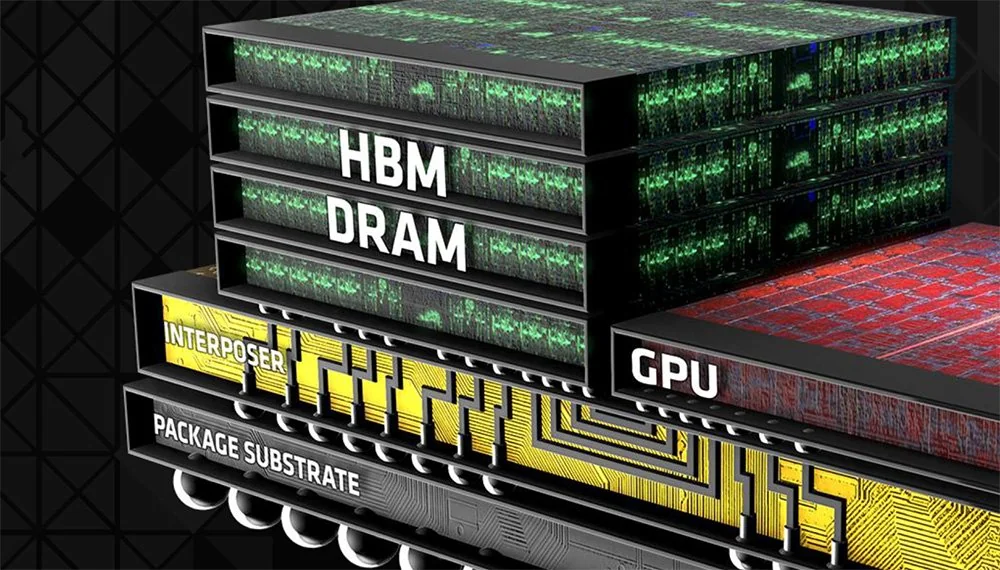

高带宽内存 4(HBM4)作为 3D 堆叠内存技术,即将为 AI 领域带来前所未有的变革。今年早些时候,JEDEC 最终确定了用于高性能 AI 的 HBM4 内存标准。新版本在性能上实现了重大突破,相比前代 HBM3,它提供了更高的单引脚速度和接口宽度,目标是在 2,048 位接口上实现每引脚 8 Gbps 的传输速度,每个内存堆栈的带宽达到 2 TB/s,大约是当前 HBM3 芯片带宽的两倍。

在容量方面,HBM4 也大幅提升,支持高达 16 层的堆叠,每个芯片密度为 24 Gb 或 32 Gb,每个堆叠最高可达 64 GB,单个 HBM4 模块容纳的数据量相当于目前高端 GPU 的整个显存容量。同时,HBM4 在设计上兼顾了能效,允许更低的 I/O 电压和核心电压,这对于需要不断在 GPU 之间移动 TB 级数据的生成式 AI 训练和大型推荐系统运行至关重要。

供应挑战:三家供应商角逐量产

目前,仅有 SK 海力士、美光和三星三家内存供应商具备批量生产 HBM4 所需的 DRAM 和 3D 堆叠专业知识,它们的量产能力将直接影响英伟达、AMD 和博通等公司未来 GPU 和 AI 加速器的硬件路线图。

SK 海力士无疑是 HBM4 领域的领跑者。该公司早在 2015 年就为 AMD GPU 供应了第一代 HBM,并在后续的 HBM2、HBM2E 和 HBM3 方面一直领先。根据 Counterpoint Research 的数据,2025 年第二季度,SK 海力士市场份额高达 62%,远远领先于竞争对手。其优势源于与英伟达的紧密联盟。

早在 JEDEC 正式规范发布前,SK 海力士就已开始提供 HBM4 样品,并于 2025 年 3 月交付了全球首批 12 层 HBM4 样品,显示其堆叠技术已准备就绪。2025 年 9 月,该公司确认其 HBM4 已满足所有规格要求,每针运行速度为 10 GT/s,比基准的 8 GT/s 快 25%,完全符合英伟达对 Blackwell 一代 GPU 的要求。SK 海力士使用成熟的 1b DRAM 工艺制造 HBM4 DRAM 芯片,以保证较低的缺陷密度和更高的良率。截至 2025 年底,该公司已准备好在客户需要时立即提升 HBM4 的产量,预计 2026 年初开始批量出货,其 HBM4 将首先集成到 Rubin GPU 平台,并为 Blackwell GPU 提供大部分初始内存模块。2025 年第二季度,该公司 77%的销售额来自 HBM 及相关 AI 内存,市场领先地位为其带来了可观的财务收益。

美光在 HBM 领域起步较晚,但过去一年市场份额超过了三星,达到 21%。其成功主要归功于 HBM3E,它与多家客户达成供应协议,成为英伟达 AI GPU 的供应商之一。2025 年 9 月的季度报告显示,美光 HBM 业务营收已接近 20 亿美元,占公司总营收的两位数比例,且 2025 年全年的 HBM 产量已全部售罄,2026 年的订单也基本被预订一空。

2025 年 6 月,美光开始交付 HBM4 样品,为英伟达等主要客户提供了 36 GB、12 层堆栈的容量。到 2025 年第四季度,其 HBM4 样品运行速度超过每针 11 Gbps,每堆栈吞吐量超过 2.8 TB/s。美光 HBM4 预计 2026 年投入量产,已获得 2026 年价值数十亿美元的 HBM3E 订单,有望在英伟达供应链中填补 SK 海力士可能无法满足的需求空白。

三星在早期 HBM 领域落后,在 HBM3E 上困境尤为明显。SK 海力士和美光为客户量产了 8 层和 12 层 HBM3E,而三星的 12 层 HBM3E 却耗时 18 个月、多次尝试才达到英伟达的质量和性能标准,直到 2025 年第三季度才通过验证。目前,三星 HBM 仅出现在 AMD 的 MI300 系列加速器中,不过在获得英伟达认证后,已同意购买 3 万至 5 万台 12 核 HBM3E 用于液冷 AI 服务器,并将于 2025 年中期为 AMD 加速器出货。

三星试图将尖端的 1c DRAM 工艺应用于 12 层 HBM3E 和即将推出的 HBM4,但遇到了良率问题,截至 2025 年 7 月,1c 的试运行良率仅为 65%。为此,三星不得不重新校准和修改 DRAM 设计,改进基片,并增强热管理。三星计划 2026 年上半年开始量产 HBM4,2025 年第三季度已开始向英伟达交付大量 HBM4 样品用于早期认证,同时凭借与 AMD(以及 OpenAI)深化的合作伙伴关系,成为 AMD MI450 加速器 HBM4 的主要供应商。

HBM4 供应的竞争并非零和游戏,三家供应商都在竭尽全力为生成式 AI 提供高性能内存模块。2026 年将是这场内存竞赛的决定性一年,哪家供应商能率先实现量产,谁就可能成为这场竞赛的真正赢家,而押注失败者的 AI 产品计划则可能需要调整。三家供应商的成功将缓解硬性限制,提升研究人员和企业的 AI 能力,推动人工智能领域迈向新的发展阶段。